# ASV(Adaptive Supply Voltage)를 적용한 수율개선 Algorithm 제안

## The ASV(Adaptive Supply Voltage) Algorithm for Improving Yield

김준성\*, 류정수, 오현섭, 전순권, 이종필, 박현수, 최병욱, 배용태

삼성전자

mr.kim@samsung.com

### Abstract

Process variations as a percentage of speed (nominal delay) and Leakage(power consumption) are becoming more and more severe with continuing scaling of VLSI technology. Therefore, to increase the yield & stability of process, people use post silicon tuning method such as ASV(Adaptive Supply Voltage). In this paper, the algorithm of improving yields by applying ASV is presented and shows the result of elevating yield after using ASV. The proposed algorithm features finally yield up both slow process and fast process due to the use of statistical method with writing a fuse box

### I. Introduction

대부분의 SOC(System on Chip) 제품들은 동작속도와 누설전류간의 상관관계에서 서로 비례적인 관계를 취하고 있다. 즉, 동작속도가 증가하면 누설전류도 증가하고 동작속도가 감소하면 누설전류 또한 감소하게 된다.

결론적으로 대부분의 SOC제품은 특정속도이상에서 특정전류 이하를 소비할 것을 요구하므로 공정 변화에 따른 동작속도 및 누설전류가 일정 범위 수준에서 철저히 관리되어야 함을 뜻한다.

하지만, 일반적으로 신공정이 개발될수록 기존 공정보다 Channel Length 및 Vth측면을 예측하기가 어렵기 때문에 시장에서 요구되는 High Speed, Low Current의 특성을 만족하기 위해서 설계 및 특성 평가를 하기는 점점 어려워지는 것이 현실이라고 할 수 있겠다.

이에 최근 각광 받고 있는 방법이 ASV(Adaptive Supply Voltage)방법이다(이하 ASV). ASV는 저전력이 요구되는 Mobile SOC제품에 소비전력의 효율화를 위하여 널리 사용되는 기법으로 요구되는 연산속도에 따라 최적의 동작전압 및 동작주파수를 할당하는 방법이다. 현재까지의 ASV연구는 소비전력 효율화에 초점

을 맞추어 개발이 진행되어왔으나 금번 연구에서는 ASV를 이용하는 것이 제품의 수율 향상에 어떠한 영향을 줄 수 있는지 확인하는데 그 목적이 있다.

### II. Main

#### 1. Why ASV?

최근에는 Silicon이 완성된 이후에 Silicon의 특성에 따른 전압 조절로 Yield를 높이는 방법이 연구되고 있으며 이를 Post-silicon Tuning Method라고 불리고 있다. 이와 같은 Post-silicon Tuning Method로는 크게 두 가지 방법이 있는데 첫 번째로는 Transistor의 Body Bias를 조절하여 Threshold Voltage의 변화를 가져와 속도 및 Leakage를 줄이는 방법이 있는데 이를 Adaptive Body Bias(ABB)라고 칭한다. ABB의 경우 큰 약점이 있는데 그것은 Body전압을 조절하기 위한 별도의 Power-rail을 추가하여야 하므로 설계부담이 증가하고 Die-size가 증가하게 된다. 두 번째 방법으로는 전원 전압만을 조절하는 방법인데 이것이 Adaptive Supply Voltage방법이다. ASV는 추가적인 Fusing이 이루어지게 되어 Test Cost가 증가되거나 별도의 Power-rail이 필요없으므로 설계가 간단하고 Chip자체의 Overload가 생기지 않게 된다. 더욱이 최근 제품 내 기존 Laser Fuse대신 E-fuse를 삽입하는 추세이므로 Overhead감소 및 추가 Test Cost측면이 전체 Test에 미치는 영향은 더욱 감소하게 되는 장점이 있다.

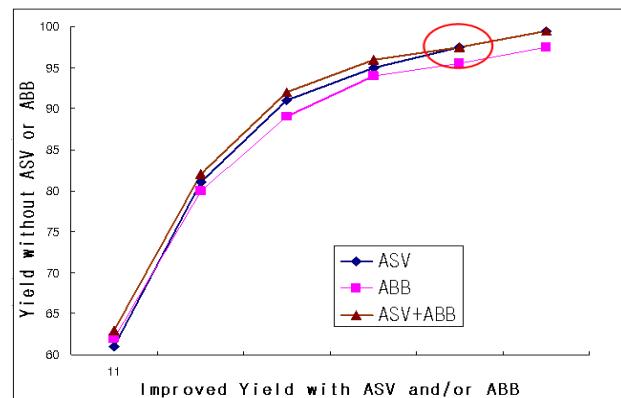

[그림 1] ABB vs ASV 적용시 수율 향상성 비교[1]

그림1은 Tom Chen. 등[1]이 실현한 ABB와 ASV를 적용했을 때의 비교 그림이다. 그럼에서 확인할 수 있듯이 ASV와 ABB방법을 동시에 수행하였을 경우 수율 향상이 가장 크게 확인되나 Yield가 70%이상 수준에서는 ASV단독으로 적용하는 경우와 효과가 같으므로 본 논문에서는 Post-silicon방법 중 비교적 수율이 좋은 제품군의 특성 및 추가 수율 향상에 더욱 유리하다고 판단되는 ASV를 중심으로 실험을 진행하였다.

## 2. Experiment Overview

본 논문에서는 ASV측정결과를 SOC내부로 Feedback하기위하여 User-ID(Customer가 Firmware등의 보안을 위해 설정한 값을 저장하기 위해 제작된 일종의 Fuse-box)를 이용하는 방법을 제안하고자 한다. 이 방법을 이용하면서 기존 ASV를 적용하려면 기본적으로 Chip상태에서 다음과 같은 전제 조건을 가지게 된다.

- 1) 전원 전압 조정이 가능한 PMIC와 PMIC/SOC간 Interface가 있어야 한다.

- 2) 변화 및 정보를 수용할 수 있는 Fuse여유분과 Fuse정보를 CPU가 읽을 수 있게 내부 버스에 연결되어 있어야 함.

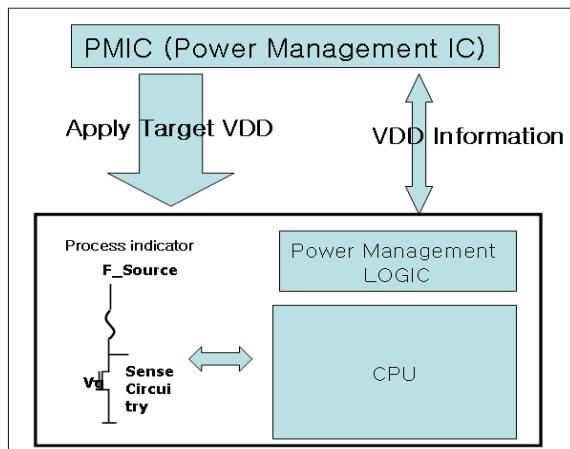

제안된 방법의 기본적인 Concept은 아래의 그림2와 같은 방법으로 설명할 수 있다.

[그림 2] ASV using Fuses as Process Variation Indicators

즉, ATE측정결과로부터 공정변화에 대한 정보를 파악하여 이를 Fuse-box에 기록한 후 PMIC를 통해 Target VDD를 설정하는 방법이다. 단, 미세 공정에서 VDD에 따라 큰 변화량을 보이는 Leakage특성이나 Speed특성 때문에 공정 변화에 따라 인가하는 Voltage의 변화량을 조정하는 일은 매우 중요하다.

본 연구에서는 공정 변화량 조정부분에 대해 품질적인 측면을 고려하면서도 수율적인 측면의 향상을 위해 기존의 임의로 Voltage를 인가하는 방식을 채택하지 않고 최대한 이론적이고 통계적인 방법을 사용하여 접근하고자 하였다.

이 실험을 위해 위의 조건이 모두 갖추어져 있는 SOC제품군중에 Modem제품군을 선정하고 이를 통해 적용 결과를 검토하였다. Modem 제품군의 경우 자체 전력소비를 줄이기 위해 전원전압 조정기능이 가능하였으며, User-ID Fuse내에 총 4개의 Dummy Fuse를 가지고 있어, 다수의 공정 변화를 기록 가능하였다. 또한 Arm을 사용하여 ATE환경에서는 Fusing값을 읽을 수 없었으나 Serial interface를 이용하여 ATE에서도 쉽게 읽을 수 있도록 하였다. 이 읽은 값을 바탕으로 최종 Package Test시에는 Fusing된 값을 ATE장비가 인식하게 하여 공정 및 각 Chip별 ET값에 따라 다른 Voltage를 적용하였다.

## 3. Supply Voltage Changing Process

### 1) Finding Dominant Factor (Speed or Leakage?)

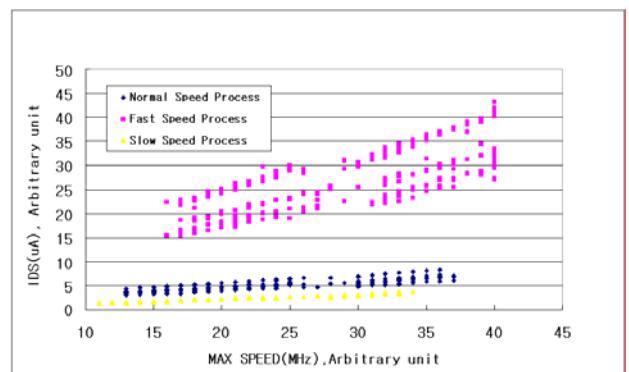

서두에서 언급한 것처럼 대부분의 제품에서 누설전류와 Speed는 비례 관계에 있다. 또한, Speed Parameter를 대변할 수 있고 ATE에서 Measure할 수 있는 특성으로는 IP의 Functional Test Pattern의 Lvcc특성이 있다. 그림 3은 누설 전류에 대해서 Max Speed특성과 IDS(Leakage Current)간의 관계를 Mixed(Slow+Fast) Speed Process에서 추출하여 상관 관계를 나타낸 그림이다.

[그림 3] Leakage Current vs Speed

위의 결과와 같이, 대부분의 SOC공정산포는 Max Speed로 대변되는 Lvcc의 특성과 IDS간의 관계로 설명될 수 있으며 이를 최적화하는 것이 금번 실험의 첫 번째 단계이다.

결국 Device의 특성을 나눌 때 이 제품이 Leakage(=IDS)에 Dependent한지 LVCC(=Speed)

특성에 Dependent 한지를 우선 구분해야 한다.

## 2) Finding dependence (Speed or Leakage?)

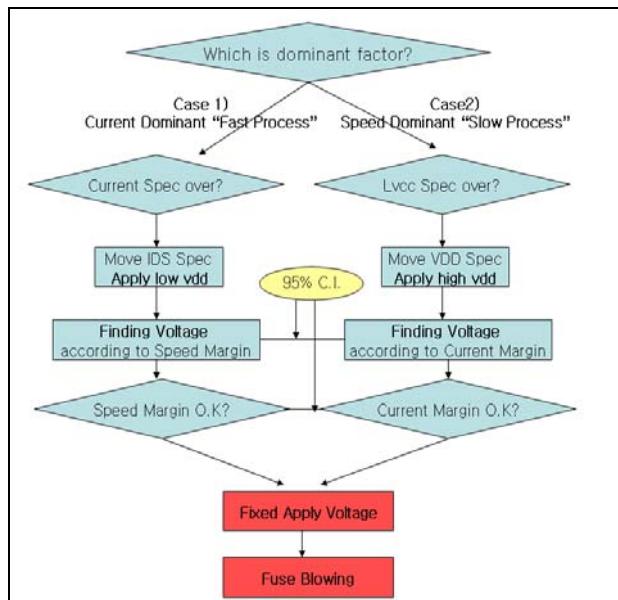

본 실험에서 적용된 Dominant Factor를 찾는 전반적인 Test Sequence를 아래 그림 4에 도시하였다.

[그림 4] Example of ASV by Leakage Dependent Process

즉, Dominant한 Factor를 찾고(실제로는 Slow Process인지, Fast Process인지 찾는 과정), 이후 판단된 결과에 따라서 각각의 진행 방식을 결정하는 방식을 제안한다.

Low VDD를 인가하는 방법이나 안정된 Speed Margin을 찾는 방법은 95%신뢰구간을 적용하는 방법을 적용하였다(95%신뢰구간이란 이 Voltage를 적용하였을 경우 Pass할 확률이 95%이상이라는 뜻).

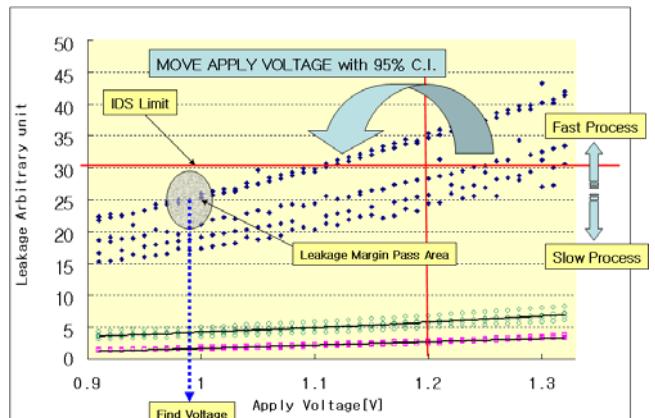

Current 혹은 Lvcc 각 경우에 대해 하나의 진행 예시를 설명하기 위해 Dominant Factor가 Leakage로 설정되었을 경우에 아래 그림 5,6에 자세히 설명하였다 그림 5에 설명된 것은 Wafer Test시 인가된 VDD=1.2V를 우선적으로 적용한 후 이때의 제품 Current Limit인 30(A.U.)를 Spec Over했을 경우를 도시한 것이다. 이때의 VDD는 Spec in을 위하여 기준보다 적은 값으로 인가되어야 하며, 이때 IDS측정된 구간인 값에 따라서 95%신뢰구간을 적용할 수 있는 Vdd인 0.90~0.99V사이로 인가되는 과정을 설명하고 있다.

즉, 제품의 Current Limit에 대해 Spec Over되는 경우에는 우선적으로 Current Spec내로 이동시키고 이때의 Voltage에 대해 Speed Margin을 순차적으로

확보해간다.

[그림 5] Detail View step 1 of ASV by L.D.P

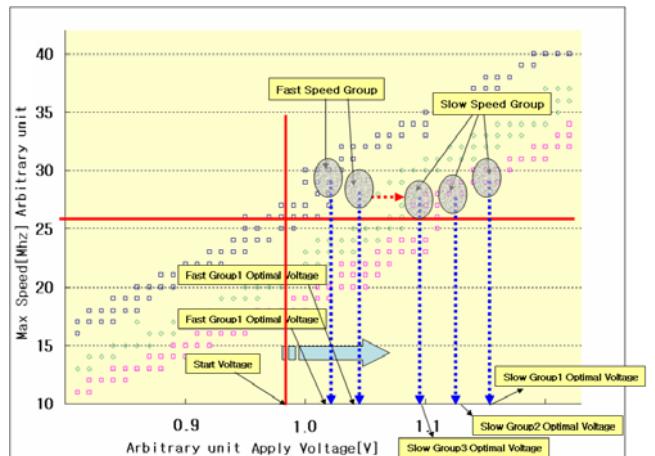

이후 그림 6에서처럼 이 Voltage에서의 Speed Margin을 확보할 경우도 95%신뢰 수준이 적용된 Speed Margin구간인 1.0~1.05V사이에서 존재함을 확인할 수 있으며 이 Voltage에서 Current Spec을 그림 5에서 재 역산하게 되면 Current Spec인 30(A.U.)이내이므로 이때의 Voltage는 ASV를 적용하기에 적당한 Voltage임을 알 수 있다.

[그림 6] Detail View step 2 of ASV by L.D.P

궁극적으로는 각 Die마다 Lvcc Search를 진행할 수 없기 때문에 Mixed Speed Process에서 선 검토된 IDS Limit에 따라 Speed 구간을 기설정 하여야 양산성 확보에 도움이 될 것이다.

## 3) Fusing Method

실험에 검토된 Fuse Box는 Dummy Bit 4bit을 이용하여 총 16개에 대해 Voltage인가 Group을 세분화하였으며 이는 제품별 동작 Voltage와 User-ID Dummy개수에 따라서 달라질 수 있다.

각각에 검토 결과에 따라서 FAST/SLOW별 세분화

Voltage를 표 2와 같이 적용하였으며 기존 연구에서 적용된 Voltage별 일괄 적용 방식이 아닌 검토 결과에 따른 적용된 Voltage 적용을 시도해 정확성을 높이고자 하였다.

|    | Optimal Voltage | Fused Bitfield[3:0] | Voltage Group   |

|----|-----------------|---------------------|-----------------|

| 1  | -0.90           | 1111                | FAST Group[4:0] |

| 2  | 0.90~0.95       | 1110                |                 |

| 3  | 0.95~1.00       | 1101                |                 |

| 4  | 1.00~1.05       | 1100                |                 |

| 5  | 1.05~1.10       | 1011                |                 |

| 6  | 1.10~1.15       | 1010                |                 |

| 7  | 1.15~1.20       | 1001                |                 |

| 8  | 1.20~1.25       | 1000                |                 |

| 9  | 1.25~1.30       | 0111                |                 |

| 10 | 1.30~1.35       | 0110                | NORMAL          |

| 11 | 1.35~1.40       | 0101                |                 |

| 12 | 1.40~1.45       | 0100                |                 |

| 13 | 1.45~1.50       | 0011                |                 |

| 14 | 1.50~1.55       | 0010                |                 |

| 15 | 1.55~1.60       | 0001                |                 |

| 16 | 1.60~           | 0000                |                 |

[표 1] Optimal Voltage vs Fusing Value

본 논문에서는 제품의 동작 Voltage를 감안하여 좀더 정확한 Voltage 구분을 위해 각 제품별 IDS를 추출한 후에 Lvcc Margin을 찾는 방법을 적용하였으나 양산 단계의 제품들은 양산시 편의를 위하여 Correlation된 IDS값을 적용하는 것을 권장한다.

|       | Supply Voltage | Slow Group<br>(Group 1~6) | Normal Group | Fast Group<br>(Group 1~6) |

|-------|----------------|---------------------------|--------------|---------------------------|

| WAFER | Leakage Test   | TYPICAL                   |              |                           |

|       | LVCC Test      | LVCC                      |              |                           |

| PKG   | Leakage Test   | 1.50~1.80                 | TYPICAL      | 1.05~1.25                 |

|       | LVCC Test      | 1.30~1.60                 | LVCC         | 0.85~1.05                 |

[표 2] Supply voltage for ATE Test

#### 4) Yield Improvement

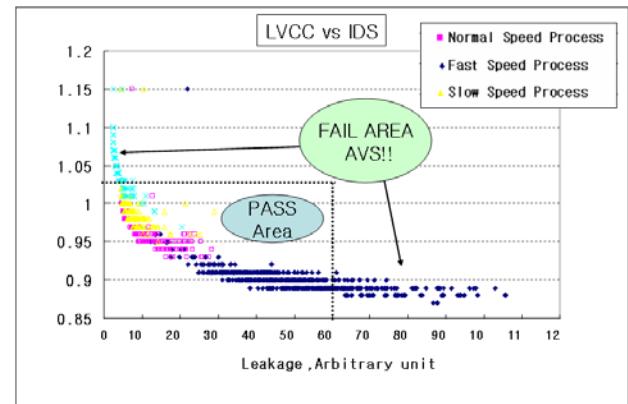

제안된 방법의 Feasibility를 검증하고 수율을 확인하기 위하여 제품의 Mixed Process Lot에 해당하는 Wafer 3매로 검증을 실시하였다. 상기 Lot의 통계적 특성을 확인하기 위하여 전체 샘플에 대하여 전원 전압을 각각의 특성에 맞게 변화시키면서 LVCC와 전압 변화에 따른 누설전류를 측정하였다.

AVS를 적용하지 않았을 경우에는 1.08V이상이어야 정상이고 누설전류는 60(A.U.)를 넘지 말아야 한다고 가정하였다. 따라서 그림 7의 경우처럼 많은 부분 Fail이 발생할 여지가 있으며, AVS를 적용할 수 있는 부분도 많아질 수 있다.

[그림 7] Minimum Lvcc vs Current at Mixed Speed Process

Table 3은 Table 2의 Fusing값을 토대로 ATE에서 전원 전압을 변경하여 최종적으로 측정한 Yield이다.

|              | Without AVS |            | With AVS |            |

|--------------|-------------|------------|----------|------------|

|              | Yield       | Major Fail | Yield    | Major Fail |

| Slow Process | 40%수준       | Bist Lvcc  | 85%수준    | Bira       |

| Fast Process | 7%수준        | Leakage    | 14%수준    | Leakage    |

[표 3] Supply voltage for ATE Test

SS Corner의 경우 AVS를 적용하기 전에 45.9%의 Yield를 보였으며 주 원인은 LVCC Margin부족이었으나 AVS를 적용하여 LVCC에 의한 Fail은 대부분 처리할 수 있었으며 실제로 AVS를 적용한 후에는 수율이 약 45% 향상되어 Total 85%의 향상된 수율을 나타내었다. Fast Process Corner의 경우에는 누설전류에 의한 Fail이 많았으며, AVS를 적용한 후에는 약 7%의 수율 향상이 있었다. 본 제품의 경우 ASV 적용 전 분포도에 의해 Leakage에 의한 영향은 크게 기대되지 않았으나 Leakage Dependent한 제품에 따라서는 보다 좋은 결과도 예상된다.

### III. Result

ASV에 대한 연구 결과 다음과 같은 결론을 얻을 수 있었다.

I. PMIC와 PMIC/SOC간 Interface를 통해 공정 수준에 맞는 최적의 Voltage를 인가하는 ASV(Adaptive Supply Voltage)방법이 적용되었으며, SOC내부로 Feed-back하는 System으로는 제품 내 User-ID에 Fusing하는 방법을 사용하였다.

II. 공정 변화에 따른 불량률을 최소화하기 위해 적용한 AVS의 검토 결과, 적용 대상을 Current

Dependent Process(Fast Process)와 Speed Dependent Process(Slow Process)로 나눌 수 있었으며 각각에 대한 수율을 향상시키기 위해 Current Dependent Process의 경우에는 Voltage Down, Speed Dependent Process의 경우에는 Voltage Up을 진행한 후 각각의 Margin을 재 설정함으로써 수율을 관리할 수 있었다.

III. 이론의 실제 검증을 위해 실제 구현이 가능한 Modem제품군을 통해 Mixed Speed Process 공정을 통해 실험한 결과, Current Dependent Process에서는 약 7%, Speed Dependence Process에서는 약 45%의 수율 향상을 보였으며 이를 실장에서 재 검증한 결과도 불량현상이 없어, ATE TEST 시에 적용이 가능함을 확인하였다.

## References

- [1] Tom Chen and Samuel Naffziger, "Comparison of Adaptive Body Bias and Adaptive Supply Voltage for Improving Delay and Leakage under the Presence of Process Variation", IEEE Transaction on very large scale integration systems, VOL11, No5 2003 IEEE

- [2] G.Wei,J.kim etc, "A variable frequency parallel I/O interface with adaptive power supply regulation." IEEE ISSCC Dig.Tecg.Papers, Feb.2000, pp298–299

- [3] T.Burd etc,"A Dynamic Voltage Scaled Microprocessor System," IEEE Journal of Solid Stage Circuit, vol35,no.11,pp1571–1580, Nov,2000.

- [4] G-Y Wei and M. Horowitz, "A fully digital, energy-efficient, adaptive power-supply regulator, "IEEE J. Solid-State Circuits, Vol. 34, PP,520–528, Apr,1999

- [5] J.Kim and R, Horowitz, "An efficient digital sliding controller for adaptive power supply regulation," Proc.2001 Symp. VLSI Circuits Dig. Tech. Paper, June 2001, pp.133–136.

- [6] H.C.Wan et al. "Chanel doping engineering of MOSFET with adaptable threshold voltage using body effect for low voltage and low power applications," in Proc. 1995 Int. Symp. VLSI Technology, Systems, and Applications, 1995, pp.1590–163